24小時(shí)聯(lián)系電話:18217114652、13661815404

中文

公司新聞

-

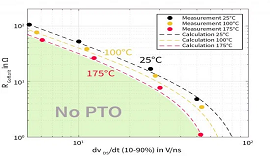

說明 SiC MOSFET 在電力電子領(lǐng)域的優(yōu)勢

SiC MOSFET 的低導(dǎo)通和開關(guān)損耗是設(shè)計(jì)工程師需要在更高電壓下實(shí)現(xiàn)高工作頻率的關(guān)鍵因素。這為電力電子應(yīng)用(例如快速電池充電器和伺服驅(qū)動(dòng)器)的設(shè)計(jì)人員帶來了許多優(yōu)勢。然而,碳化硅 MOSFET 會(huì)因 PTO 事件而遭受更大的損失,因此需要仔細(xì)選擇器件和驅(qū)動(dòng)電路設(shè)計(jì)以減輕這些影響。器件對 PTO 的敏感性可以從數(shù)據(jù)表參數(shù)中估算出來,但可以使用合適的評估板進(jìn)行更全面的表征。

- 查看詳細(xì)

-

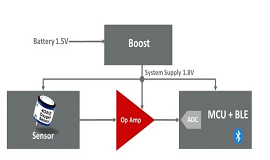

傳感器能效推動(dòng)系統(tǒng)的未來

在支持 AI 系統(tǒng)的傳感器網(wǎng)絡(luò)中,創(chuàng)新正在許多不同的層面上發(fā)生。尤其是 IC 制造商正在開發(fā)低功耗傳感器構(gòu)建模塊,以幫助當(dāng)今的工程師創(chuàng)建未來更智能、更高效的系統(tǒng)。

- 查看詳細(xì)

-

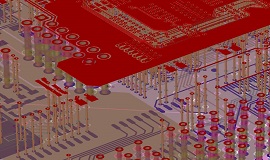

布局中板層的PCB堆疊技術(shù)

電路板層堆疊變化將影響電路板的可制造性和成本。 在配置層堆疊時(shí)要考慮的信號和電源完整性細(xì)節(jié)。 不同的 PCB 堆疊技術(shù)以及您的設(shè)計(jì)工具如何幫助您實(shí)現(xiàn)目標(biāo)。

- 查看詳細(xì)

-

通過阻抗平衡降低電源中的 CM 噪聲

在緊湊空間中運(yùn)行的簡單開關(guān)穩(wěn)壓器電路(例如在小型 PCB 上)通常可以部署在嘈雜的環(huán)境中,而不會(huì)在輸出功率電平上疊加明顯的噪聲。只要您正確布置電路板,您可能只需要一個(gè)簡單的濾波器電路來消除輸入和輸出上的 EMI。隨著穩(wěn)壓器在物理上和電氣上變得更大,噪聲問題會(huì)變得更加明顯,即 PCB 布局中的輻射 EMI 和傳導(dǎo) EMI。

- 查看詳細(xì)

-

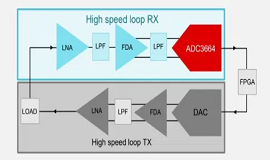

工業(yè)設(shè)計(jì)中的實(shí)時(shí)控制和高精度數(shù)據(jù)采集

降低設(shè)計(jì)復(fù)雜性的其他系列功能包括片上抽取選項(xiàng),使設(shè)計(jì)人員能夠輕松去除系統(tǒng)中不需要的噪聲和諧波,并將 SNR 和無雜散動(dòng)態(tài)范圍提高多達(dá) 15 dB。這些抽取選項(xiàng)和互補(bǔ)金屬氧化物半導(dǎo)體 (CMOS) 接口允許設(shè)計(jì)人員將這些 ADC 與基于 ARM 的處理器或數(shù)字信號處理器一起使用,而不是現(xiàn)場可編程門陣列,這有助于降低系統(tǒng)成本。

- 查看詳細(xì)